PWM设计之DAC的低通滤波器设计

2018-12-10 10:58:44 点击:

如何通过PWM实现数字到模拟量的转换,得到很多朋友们的反馈,大家都比较感兴趣的如何选用电阻和电容的值才能得到一个满意的模拟值(低纹波)?

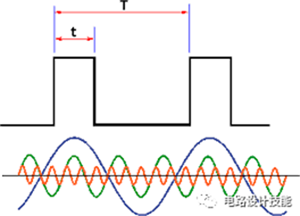

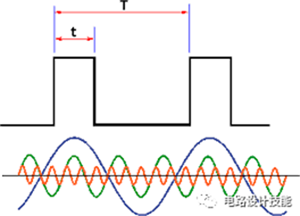

首先我们看一下脉冲信号的频谱,根据傅立叶变换,周期为T的脉冲信号可以分解为多个单频率的信号的叠加,最小的频率分量为1/T,有兴趣的同学可以通过Matlab自己做一下分析。

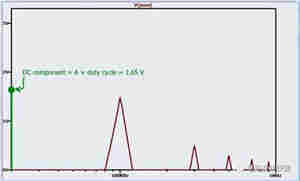

比如,我们对幅度为3.3V、周期为10uS(频率100KHz)、占空比为50%的脉冲信号(此时为方波)进行FFT变换,可以得到1.65V的直流分量、100KHz、300KHz(3次谐波)、500KHz(5次谐波)。。。等频率分量,最小的交流频率为100KHz。

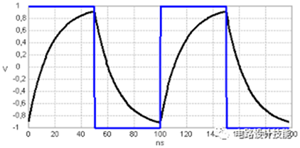

占空比为50%的脉冲信号的波形

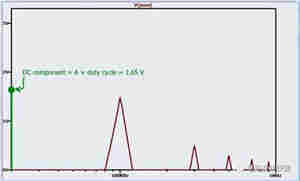

占空比为50%的脉冲信号的频谱分量

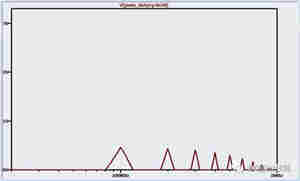

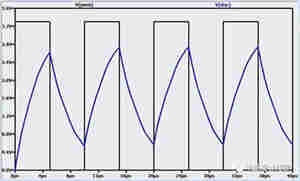

改变占空比呢?来看看占空比为10%和90%的脉冲波形经过FFT之后的交流频率分量

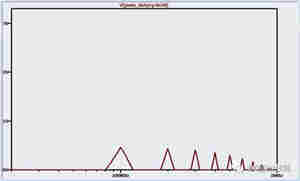

占空比为10%的脉冲的频率分量

从以上简单的分析可以看出,无论占空比是多少,脉冲波形除了直流分量以外,交流部分的最低频率都为脉冲的重复频率100KHz上,在DC和脉冲重复频率100KHz之间一马平川,光秃秃的。

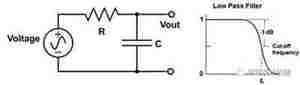

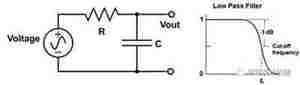

因此,如果要得到直流分量,只需要去掉100KHz以上的频谱能量就可以了。最简单的方法就是通过由一个电阻R和一个电容C构成的一阶低通滤波器,其截止频率为fc=1/2*Pi*R*C,我们要得到的是直流分量,滤除的是100KHz以上的频率,因此只要截止频率在100KHz以内,并且能对100KHz以上的所有频谱都有较好的抑制,就能够得到比较好的DC输出。

LPF电路构成和频率响应

RC电路的时域响应

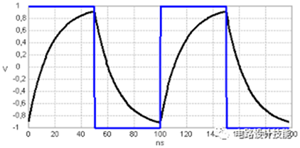

可以想象,截止频率越高,越是接近要滤除的频率(比如50KHz之于100KHz),该滤波器对100KHz的滤波效果就较差,就会有一定量的残余能量出现在滤波器的输出端,如下图,也就是输出的波形纹波比较高。

对脉冲频率为100KHz的信号进行截止频率为50KHz的低通滤波得到的输出信号,纹波比较高

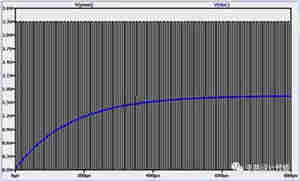

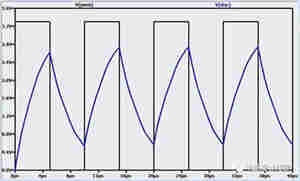

如果降低截止频率,越是接近直流,从而距离要滤除的频率越远,比如针对100KHz的脉冲频率选择1KHz作为LPF的截止频率,则在100KHz处可以达到非常高的抑制度,100KHz的残留就非常小,也就是在输出的直流信号上的纹波可以变得很小,见下图。

截止频率为1KHz的低通滤波器的建立时间很长 ~ 1ms

但却出现了另外一个问题 - 需要花费很久的时间(学名叫建立时间 setting time)才能达到应该达到的DAC的直流值。原因就是fc低,意味着RC更高,也就是充电的时间常数变得很长 - R增大意味着对C进行充电的电流变小,要对C冲电到一定的值花费的时间也就更久。,

因此这就出现了一个让人纠结的选择:

选择较低的截止频率 - 较低的纹波,较长的建立时间

选择较高的截止频率 - 较大的纹波,较快的建立时间

你会说一阶不够,要不多用几阶滤波器,加上电感或者有源的运放来进行低通滤波,这确实能改善滤波的效果,但 -- 电路的复杂度增加、元器件成本增加了,且改善有限。

那不增加电路的复杂程度,还是只用这一个R和一个C是否能够改善性能呢?

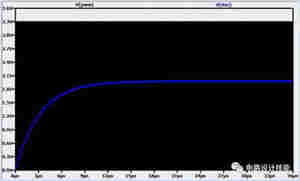

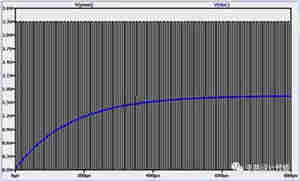

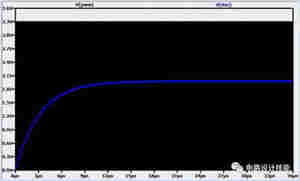

答案是肯定的,其实也很简单 - 把交流分量的频率踢的远远的,在保持较低的时间常数(建立时间短)的情况下,将LPF的截止频率fc和要滤除的脉冲重复频率之间的间隔尽可能的拉开,比如将100KHz的重复频率给踢到10MHz(出去100倍),占空比不变,如果用原来的50KHz的滤波器,到了10MHz的地方怎么也把10MHz以上的频率给消灭的只剩下一点渣了。看下图,直流建立时间大约为15µs, 纹波变得只有25mV左右了。

用截止频率为50KHz的RC得到的建立时间大约为15µs

用截止频率为50KHz的RC对10MHz的脉冲信号进行LPF得到的纹波

是不是很神奇?其实理论依据很简单,自己把低通滤波器的频响曲线画一下就很容易理解了。

到这里我们就应该知道如何设计自己的PWM系统的各项参数来构造一个简单好用的DAC。

首先我们看一下脉冲信号的频谱,根据傅立叶变换,周期为T的脉冲信号可以分解为多个单频率的信号的叠加,最小的频率分量为1/T,有兴趣的同学可以通过Matlab自己做一下分析。

比如,我们对幅度为3.3V、周期为10uS(频率100KHz)、占空比为50%的脉冲信号(此时为方波)进行FFT变换,可以得到1.65V的直流分量、100KHz、300KHz(3次谐波)、500KHz(5次谐波)。。。等频率分量,最小的交流频率为100KHz。

占空比为50%的脉冲信号的波形

占空比为50%的脉冲信号的频谱分量

改变占空比呢?来看看占空比为10%和90%的脉冲波形经过FFT之后的交流频率分量

占空比为10%的脉冲的频率分量

从以上简单的分析可以看出,无论占空比是多少,脉冲波形除了直流分量以外,交流部分的最低频率都为脉冲的重复频率100KHz上,在DC和脉冲重复频率100KHz之间一马平川,光秃秃的。

因此,如果要得到直流分量,只需要去掉100KHz以上的频谱能量就可以了。最简单的方法就是通过由一个电阻R和一个电容C构成的一阶低通滤波器,其截止频率为fc=1/2*Pi*R*C,我们要得到的是直流分量,滤除的是100KHz以上的频率,因此只要截止频率在100KHz以内,并且能对100KHz以上的所有频谱都有较好的抑制,就能够得到比较好的DC输出。

LPF电路构成和频率响应

RC电路的时域响应

可以想象,截止频率越高,越是接近要滤除的频率(比如50KHz之于100KHz),该滤波器对100KHz的滤波效果就较差,就会有一定量的残余能量出现在滤波器的输出端,如下图,也就是输出的波形纹波比较高。

对脉冲频率为100KHz的信号进行截止频率为50KHz的低通滤波得到的输出信号,纹波比较高

如果降低截止频率,越是接近直流,从而距离要滤除的频率越远,比如针对100KHz的脉冲频率选择1KHz作为LPF的截止频率,则在100KHz处可以达到非常高的抑制度,100KHz的残留就非常小,也就是在输出的直流信号上的纹波可以变得很小,见下图。

截止频率为1KHz的低通滤波器的建立时间很长 ~ 1ms

但却出现了另外一个问题 - 需要花费很久的时间(学名叫建立时间 setting time)才能达到应该达到的DAC的直流值。原因就是fc低,意味着RC更高,也就是充电的时间常数变得很长 - R增大意味着对C进行充电的电流变小,要对C冲电到一定的值花费的时间也就更久。,

因此这就出现了一个让人纠结的选择:

选择较低的截止频率 - 较低的纹波,较长的建立时间

选择较高的截止频率 - 较大的纹波,较快的建立时间

你会说一阶不够,要不多用几阶滤波器,加上电感或者有源的运放来进行低通滤波,这确实能改善滤波的效果,但 -- 电路的复杂度增加、元器件成本增加了,且改善有限。

那不增加电路的复杂程度,还是只用这一个R和一个C是否能够改善性能呢?

答案是肯定的,其实也很简单 - 把交流分量的频率踢的远远的,在保持较低的时间常数(建立时间短)的情况下,将LPF的截止频率fc和要滤除的脉冲重复频率之间的间隔尽可能的拉开,比如将100KHz的重复频率给踢到10MHz(出去100倍),占空比不变,如果用原来的50KHz的滤波器,到了10MHz的地方怎么也把10MHz以上的频率给消灭的只剩下一点渣了。看下图,直流建立时间大约为15µs, 纹波变得只有25mV左右了。

用截止频率为50KHz的RC得到的建立时间大约为15µs

用截止频率为50KHz的RC对10MHz的脉冲信号进行LPF得到的纹波

是不是很神奇?其实理论依据很简单,自己把低通滤波器的频响曲线画一下就很容易理解了。

到这里我们就应该知道如何设计自己的PWM系统的各项参数来构造一个简单好用的DAC。

- 上一篇:电容可有可无?运放反向输入端的电容是否有电流通过 2018/12/17

- 下一篇:PWM设计之用1根管脚、1个电阻和1个电容实现DAC 2018/12/10